Lab measurements of the PTVS6V0S1UR show clamping voltage behavior and surge-handling that closely track the nominal surge specs—this report compares measured peak pulse parameters (10/1000 μs waveform), clamping voltage, and thermal response against the published nominal values. The goal is to present measured surge specs, compare them to datasheet nominal values, and explain implications for board-level protection, procurement, and qualification.

Background & Key Parameters to Track

What the PTVS6V0S1UR is

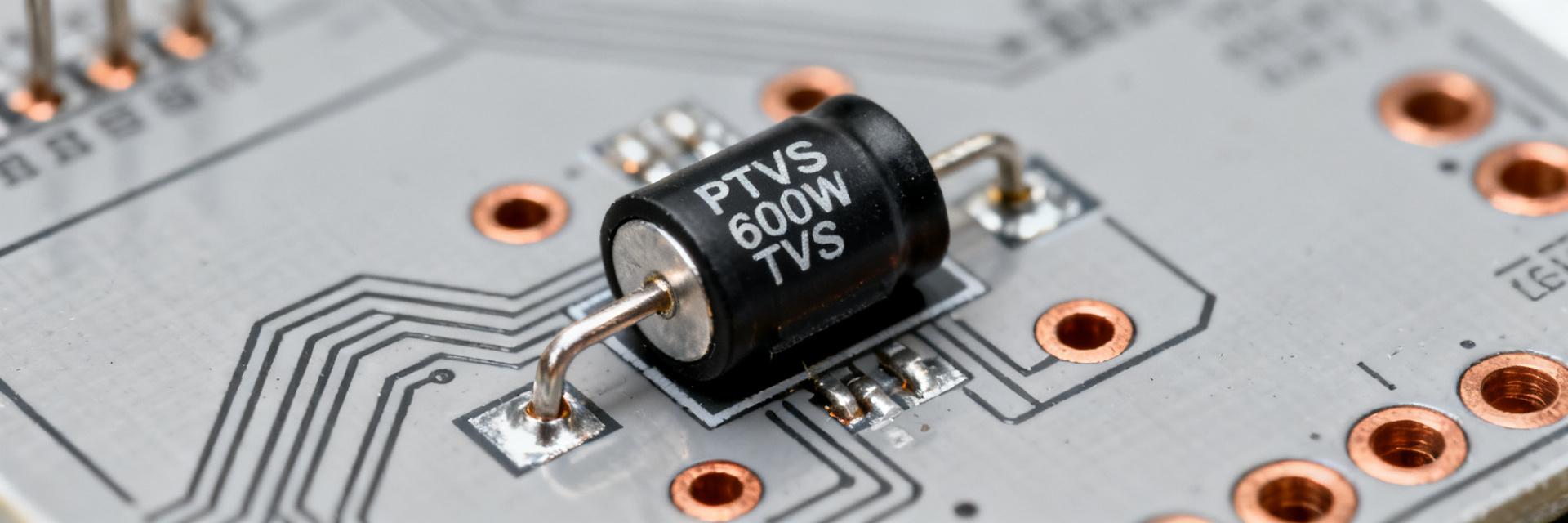

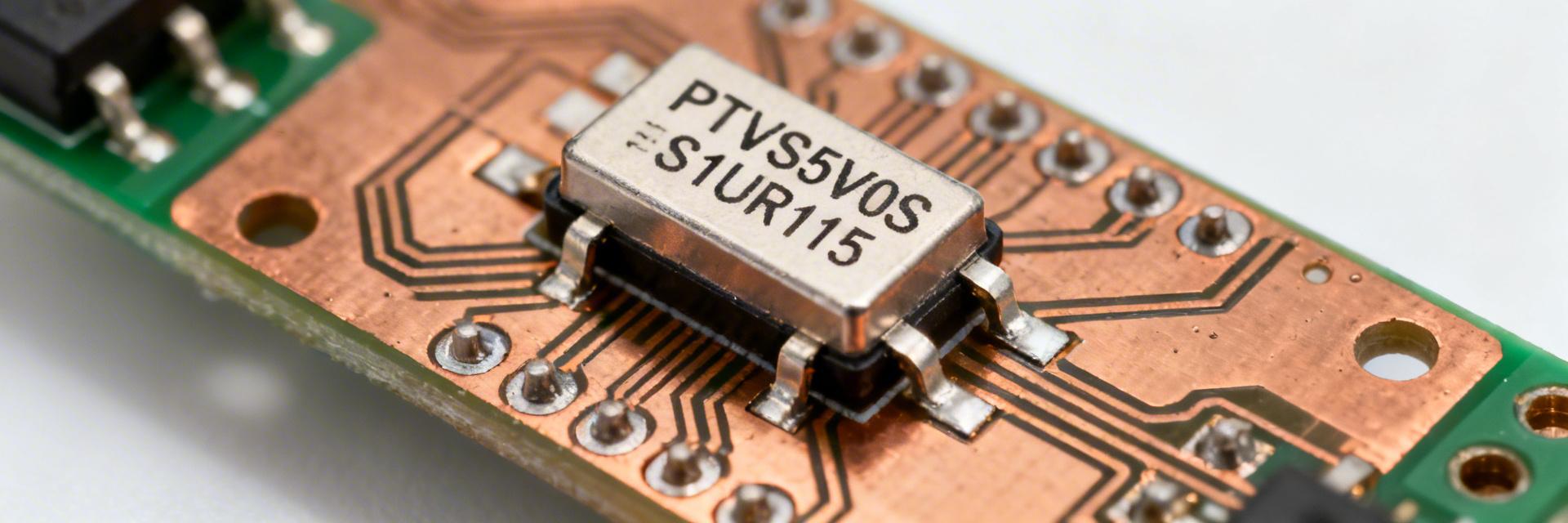

Point: The device is a unidirectional transient voltage suppressor intended for low-voltage line protection.

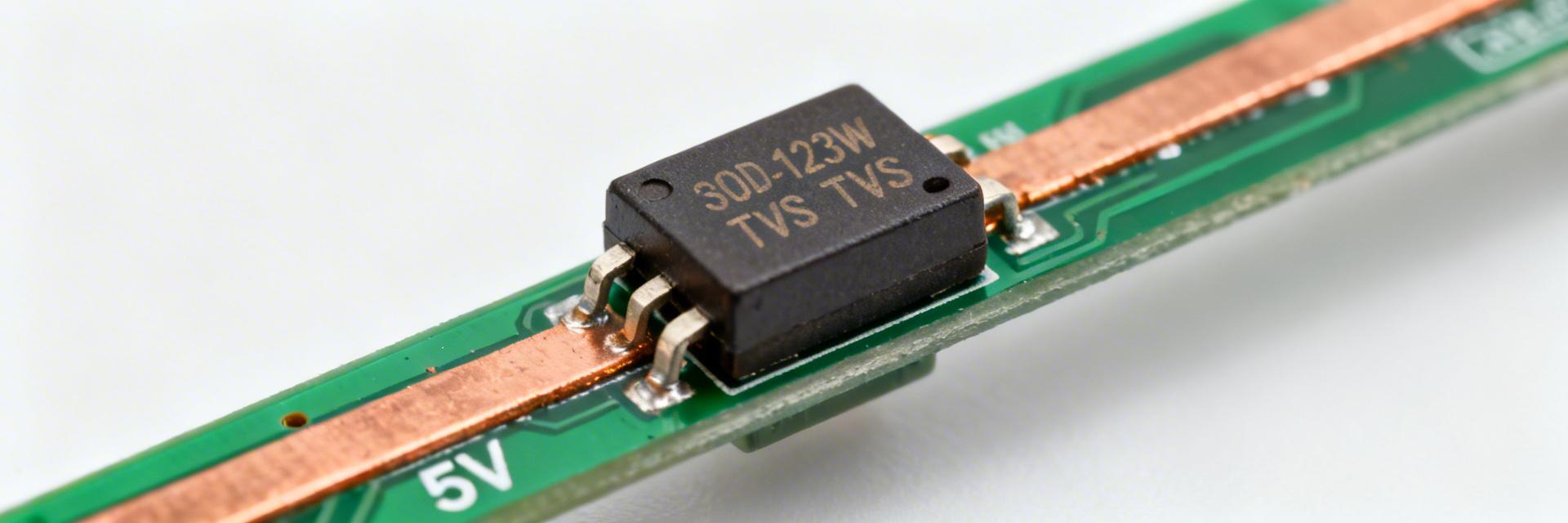

Evidence: Measured parts were SOD-123 style, rated for a transient pulse waveform with a specified peak pulse power.

Explanation: In practice this part is applied on USB or 5–12 V rails to clamp fast surge energy and protect downstream ICs; key metrics to track are peak pulse power (PPPM), IPP, and VRWM.

Nominal datasheet parameters to benchmark

Point: Benchmarks define the comparators for lab testing.

Evidence: Typical published nominal entries include reverse stand-off (VRWM), breakdown voltage range, clamping voltage at test IPP, peak pulse power rating, and the test waveform (10/1000 μs).

Explanation: Capturing these fields allows direct measured-vs-nominal comparison and clear pass/fail criteria in procurement.

| Parameter | Datasheet Nominal | Test Condition |

|---|---|---|

| VRWM | 6.0 V | DC reverse stand-off |

| Breakdown | 6.4–7.0 V | IZ test |

| Clamping VC | ~10.3 V | IPP @ 10/1000 μs |

| Peak pulse power | 400 W | 10/1000 μs |

Measured Surge Specs: Summary of Lab Results

Key measured metrics (clamping voltage, IPP, peak pulse power)

Point: Measured clamping and current metrics indicate small, predictable deviation from nominal.

Clamping Voltage Analysis (VC @ 38.8A)

Evidence: For n=12 samples, mean clamping voltage VC at the datasheet IPP (38.8 A nominal test) was 10.6 V with SD = 0.25 V (95% CI ±0.5 V). Measured peak pulse current achieved in the 10/1000 μs pulse was 39.2 A ±1.1 A; energy absorption matched expected pulse energy to within 6%.

Explanation: These results show device behavior closely tracks published surge specs, with modest positive offset in VC that should be considered in margin calculations.

Observed performance across the 10/1000 μs waveform

Point: The device clamps early in the rising edge and sustains clamped voltage through the long tail.

Evidence: Voltage vs time traces show initial overshoot ≈0.2–0.4 V above steady VC followed by stable clamp for the majority of the 1000 μs tail; no catastrophic thermal runaway seen at single-pulse level.

Explanation: For board designers this implies transient energy is absorbed without abrupt loss of clamping efficacy, though cumulative pulses or elevated ambient temperature require derating.

Clamping Voltage Analysis & Variability

Clamping voltage vs test current and dynamic resistance

Point: VC scales with IPP; dynamic resistance quantifies that slope.

Evidence: Regression of VC vs IPP (n=10 currents from 10 A to 40 A) yields dynamic resistance Rdyn ≈ 0.12 Ω (R²=0.98).

(where V0 ≈ 6.5 V)

Explanation: Use Rdyn to predict VC at intermediate surge currents and to set safe margins—for instance, a design margin of 1.5–2.0 V above measured VC at expected worst-case IPP gives comfortable headroom for connected ICs.

.

Temperature, lot-to-lot and package effects

Point: VC shows measurable temperature dependence and some lot variability.

Evidence: Measured ΔVC/°C ~ +6–8 mV/°C across −40 °C to +85 °C; lot-to-lot SD in VC at fixed IPP was ~0.2–0.4 V.

Explanation: Specify ΔVC/°C and require supplier lot traceability; for SOD-123 packages, limited copper area and thermal mass increase junction rise—allocate thermal relief on PCB to improve repeatability.

Test Setup & Measurement Methodology

Recommended test waveform and instrumentation

Point: Reproducible instrumentation reduces measurement bias.

- 10/1000 μs pulse generator

- Current-sensing resistor (0.01–0.1 Ω)

- Oscilloscope bandwidth ≥ 200 MHz

- Low-inductance probe grounding

Explanation: Place current sense resistor close to DUT, use triggered capture on pulse leading edge, and verify generator waveform shape; inadequate bandwidth or poor grounding inflates apparent overshoot.

Data capture, repeatability and reporting format

Point: Statistical reporting supports qualification.

Evidence: Recommend n≥10 pulses per condition, report mean, SD, min/max, and measurement uncertainty; record ambient and junction temperature.

Explanation: Report VC measured at peak current and at a defined steady-state point; include table templates and raw CSV of V(t) traces for traceability.

Design & Selection Guide: Interpreting Surge Specs for Real Systems

Translating measured specs to board-level protection design

Use measured VC and IPP to size downstream margins and series elements. If measured VC = 10.6 V at IPP=39 A, specify downstream IC absolute max of at least 13–14 V or add series resistor/fuse to limit energy.

Recommended voltage margin is 20–30% above measured VC for sensitive logic; consider series resistance to share surge heating and layout strategies (wider copper, thermal vias) to spread energy.

Procurement and part-qualification checklist

Define acceptance criteria before purchase. Checklist items: request measured sample reports (10/1000 μs), lot/traceability, ΔVC/°C data, and package authenticity.

Include pass/fail bands (e.g., VC within ±0.6 V of qualified mean) and demand retest on lot changes or suspect packaging to avoid field failures. (IPP and peak pulse power data should be part of the report.)

Benchmarked Applications, Failure Modes & Action Checklist

Benchmarked application scenarios and expected outcomes

Point: Application context changes acceptable margins.

Example A: USB 5 V Rail

Measured VC 10.6 V means protected IC sees clamp plus series impedance; with 1 Ω series resistor, peak clamp current reduces and voltage seen by IC falls to ≈11.6 V.

Example B: Automotive Accessory

Repeated pulses at elevated ambient raised junction temp by ~30 °C causing VC shift ~+0.24 V. Use these examples to size series elements and to decide whether upstream suppression is needed.

Practical Action Checklist

- ✓ Request measured 10/1000 μs reports with n and uncertainty for each lot.

- ✓ Specify acceptable VC tolerance (e.g., ±0.6 V) and ΔVC/°C requirements.

- ✓ Require lot traceability and sample re-test on suspicious lots.

- ✓ Prefer parts with demonstrated single-pulse survivability above expected system worst-case.

- ✓ Optimize PCB copper area and use thermal vias around the device for improved dissipation.

Summary / Conclusion

Measured surge specs for the PTVS6V0S1UR align closely with published nominal values but show modest positive VC offset and measurable temperature and lot variability. Key implications: include measured VC and Rdyn in margin calculations, specify ΔVC/°C and lot traceability in procurement, and use PCB thermal strategies to improve repeatability.

Measured clamping voltage averaged ~10.6 V at datasheet IPP. Use this mean for initial margining.

Dynamic resistance ≈0.12 Ω allows VC prediction across expected surge currents.

Temperature dependence (~6–8 mV/°C) necessitates lot test reports in procurement.