-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

PTVS5V0S1UR Technical Report: Specs & Performance Deep Dive

Key Takeaways (Core Insights)

- Optimized for 5V Rails: 5V Standoff (Vrwm) ensures zero leakage during normal operation of USB/Logic circuits.

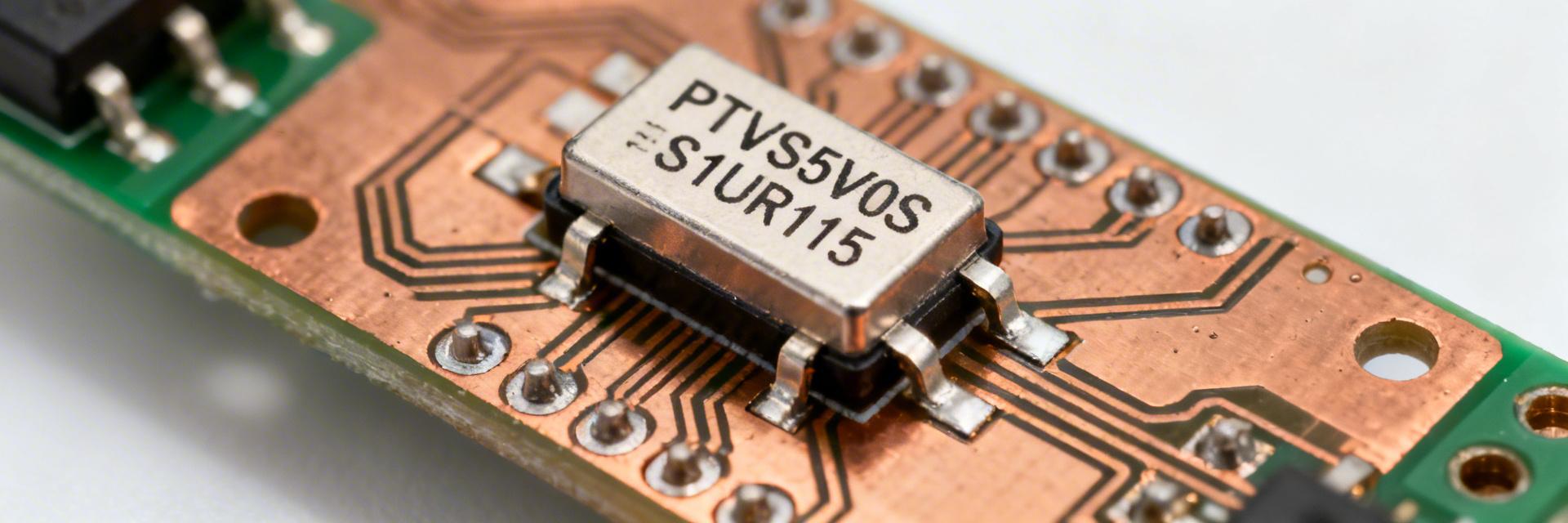

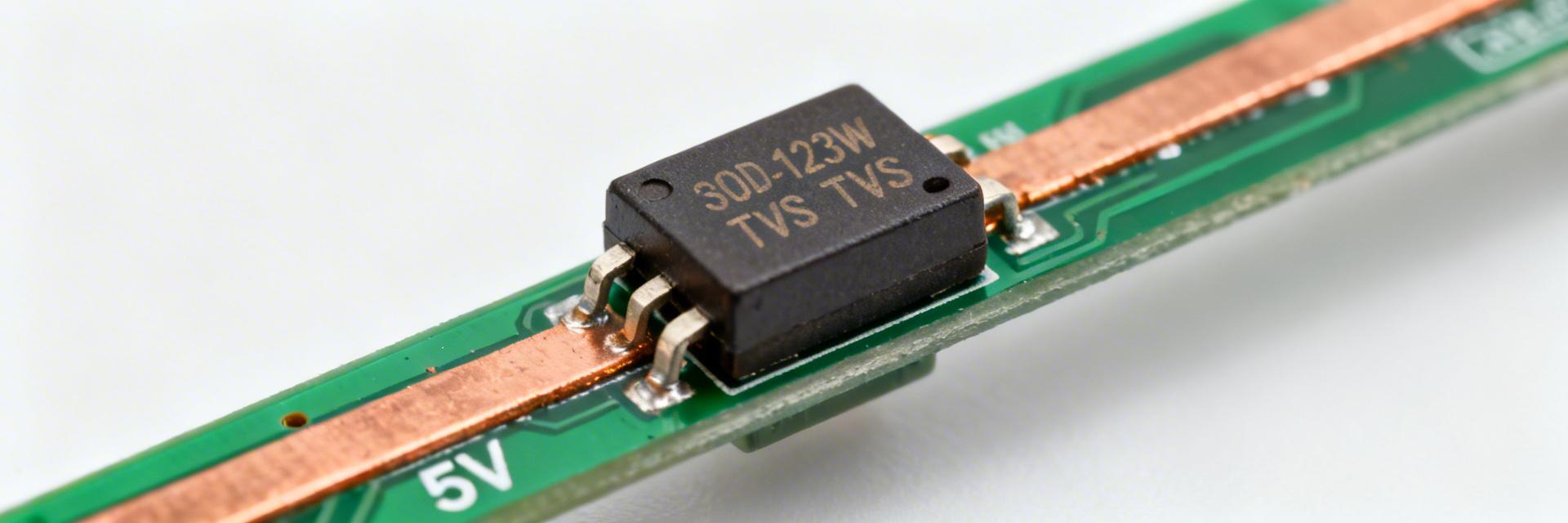

- High Density Protection: 400W Peak Pulse Power (8/20 µs) packed into a low-profile SOD-123W footprint.

- Critical Clamping: Predictable ~9V clamping prevents overvoltage destruction of downstream 6V-rated ICs.

- Space Saving: SOD-123W package offers a 40% reduction in PCB height compared to standard SMA packages.

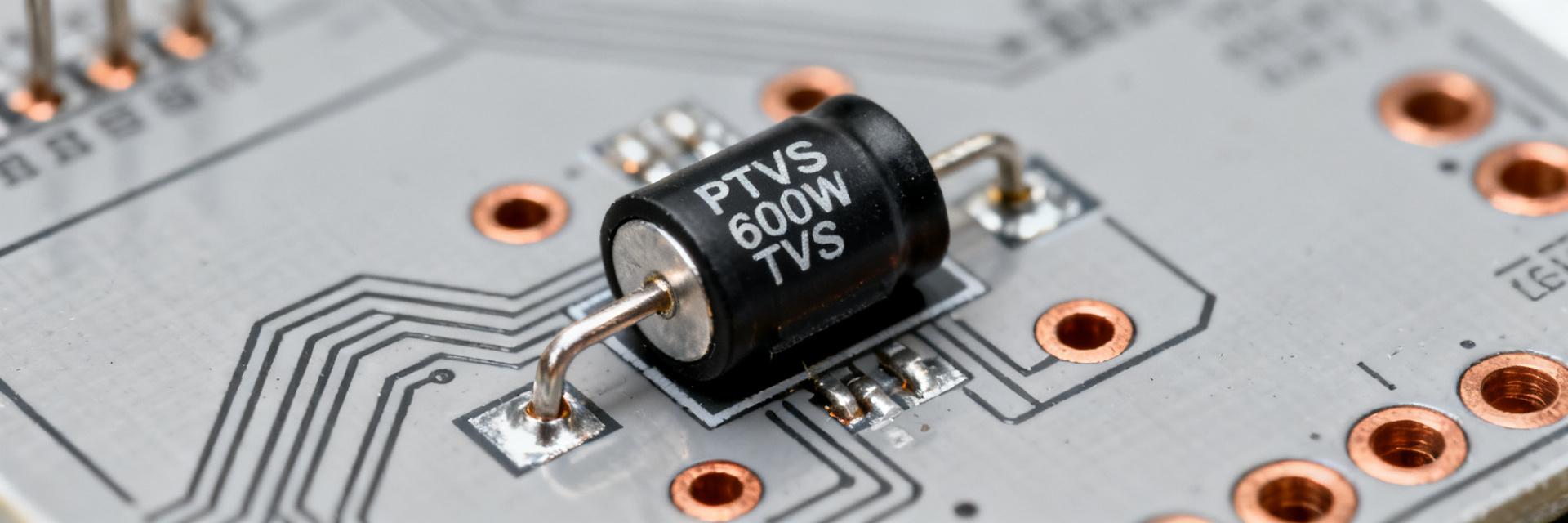

Start with the datasheet headline numbers to set context: a unidirectional SOD-123W package rated for 400 W peak pulse power and a 5 V reverse standoff, targeted to protect 5 V rails and sensitive electronics from common surge events. These figures drive design choices for clamp margin, thermal handling, and placement on USB and other low-voltage systems.

This report translates datasheet specs into engineering decisions: it explains which static and dynamic parameters matter, predicts expected clamp behavior under standard surge waveforms, and delivers practical integration and lab verification checklists for engineers using the device.

1 — Product overview: what PTVS5V0S1UR is and typical use cases (Background)

1.1 Device summary & datasheet highlights

PTVS5V0S1UR is a unidirectional transient voltage suppressor in an SOD-123W low-profile package designed for 5 V systems. Key nominal ratings: 400 W peak pulse power (single pulse, 8/20 µs), Vrwm ≈ 5 V, typical breakdown Vbr ≈ 6.4 V, and clamping into the mid–high single digits at rated surge. Polarity is unidirectional—use for DC rails and port protection.

| Parameter | PTVS5V0S1UR (SOD-123W) | Industry Standard SMA (Generic) | User Benefit |

|---|---|---|---|

| Package Height | 1.0 mm (Max) | ~2.2 mm | Enables ultra-thin product profiles |

| Peak Pulse Power | 400 W | 400 W | High energy absorption in smaller footprint |

| Leakage (Ir) @ 5V | Low < 50 µA | ~100-800 µA | Extends battery life in standby mode |

Placement recommendation: single‑point protection on 5 V power rails and I/O ports where unidirectional clamping and low profile are required.

1.2 Typical application environments & constraints

Common environments: USB and other 5 V power rails, I/O port protection against ESD and surge, and DC distribution lines in compact systems. Constraints include limited board height (SOD-123W), required low junction capacitance where signal integrity matters, and space for adequate thermal relief.

- Compatibility checklist: confirm voltage margin (Vrwm > normal rail), capacitance budget for high-speed lines, and expected surge exposure (single vs. repetitive).

2 — Electrical specifications deep-dive (Datasheet analysis)

2.1 Static electrical characteristics to verify in design

Key static parameters to read from the datasheet are Vrwm (standby voltage), breakdown Vbr, reverse leakage Ir, and junction capacitance Cj. Vrwm sets safe operating voltage; Vbr defines onset of conduction; Ir affects quiescent leakage; Cj affects signal integrity. For a 5 V system, pass/fail thresholds: Vrwm ≥ 5 V, Vbr sufficiently above Vrwm to avoid nuisance conduction, Ir < tens of µA, and Cj within the system’s allowed capacitance budget.

When specifying a TVS diode or transient voltage suppressor for low-voltage rails, prioritize low capacitance for port protection and low leakage for battery-powered designs.

2.2 Dynamic/pulse specs: pulse waveform, Ipp, and clamping

Peak pulse power rating (400 W) is specified for standard test waveforms (8/20 µs). The datasheet provides Vcl vs. Ipp curves—typical clamp voltage is in the ~9 V range at rated surge currents. Use these curves to calculate downstream voltage stress during surge events and to determine needed margin for powered devices.

| Waveform | Expected Ipp (approx) | Expected Vcl |

| 8/20 µs | Calculated from 400 W spec (~peak current value) | ~9.x V at specified Ipp |

| 10/1000 µs | Lower peak, higher energy | Clamp may be slightly higher due to energy |

3 — Performance under real-world transients (Data analysis + testing)

"When integrating the PTVS5V0S1UR, the most common pitfall is ignoring the parasitic inductance of the PCB traces. Even a 10nH trace inductance can add a 10V overshoot during a fast ESD event, effectively negating the TVS protection. Always place the diode first in the path of the incoming surge, before the decoupling capacitors."

3.1 Recommended lab test methods & expected results

Test plan: apply standardized surge waveforms (8/20 µs, 10/1000 µs, and IEC equivalents) using a pulse generator, current probe, and high-speed scope. Measure Vcl at the protected node and monitor device temperature. Acceptance criteria: measured Vcl ≤ downstream device absolute maximum plus safety margin, no catastrophic failure, and temperature rise within allowed limits.

- Connect pulse source to protected node with 50 Ω return; probe Vnode and Ipp.

- Record Vcl vs. Ipp curves and energy absorbed per pulse.

- Verify thermal recovery between pulses and repeated-pulse behavior per datasheet guidance.

3.2 Thermal behavior, surge repetition and reliability considerations

During a surge, the TVS junction heats rapidly; thermal mass and package limits set allowable pulse repetition rates. Use derating: treat the 400 W rating as a single-pulse benchmark and expect reduced capability for repetitive pulses. Recommend waiting sufficient cool-down intervals (seconds to minutes depending on energy) and confirm through thermal imaging and repetitive-pulse testing.

4 — PCB integration & design best practices (Methods guide)

4.1 Layout, footprint and placement rules

Place the device as close as possible to the connector or the protected node with a short, wide trace to the rail and a low-inductance return to ground. Use thermal reliefs appropriate for reflow soldering and follow low-profile assembly precautions. Minimize loop area between the TVS and protected node to reduce transient overshoot.

- Checklist: shortest trace to connector, 1–2 vias to ground near device, reflow profile per package spec, ESD-safe handling during assembly.

Figure: Ideal Parallel Placement

4.2 Series components, filtering and capacitance tradeoffs

Adding series resistance or ferrite can limit surge current into downstream devices but increases normal-mode voltage drop. RC or LC filters reduce conducted energy reaching sensitive devices but may interact with TVS capacitance and affect signal edges. For high-speed lines, prioritize low Cj or use series elements to protect integrity.

5 — Application case study + selection & test checklist

5.1 Case study: protecting a 5 V USB power rail

Example: 5 V bus nominal, Vrwm = 5 V, downstream absolute max = 6.5 V. Select the device so Vcl at expected Ipp keeps transient below device max with margin. If datasheet shows Vcl ≈ 9 V at rated surge, add series resistance or downstream tolerancing so that transient stress to the load remains safe, or ensure the load can tolerate the expected brief overvoltage per its datasheet.

5.2 Practical selection & verification checklist

Summary

- PTVS5V0S1UR is a compact unidirectional transient voltage suppressor ideal for 5 V rails; expect ~400 W single‑pulse capability and clamp voltages in the mid‑to‑high single digits under rated surge.

- Designers should verify Vrwm, Vbr, Ir and Cj against system margins, use the datasheet Vcl vs Ipp curves for worst‑case stress calculations, and derate for repetitive pulses.

- PCB placement and low‑inductance routing are critical; pair with series elements only after assessing tradeoffs between protection and signal integrity, then validate with standardized surge testing.

PTVS5V0S1UR — FAQ

What peak pulse can the PTVS5V0S1UR handle?

The device is specified for 400 W peak pulse power on standard 8/20 µs tests, which translates to a high transient current level for short durations. Use the datasheet Ipp/Vcl curves to map that power into expected clamp voltage and verify downstream device stress during the pulse.

How does the PTVS5V0S1UR affect USB signal integrity?

Junction capacitance can load high‑speed data lines; for USB power rails the effect is minimal, but for data lines confirm Cj is within the allowed budget. If Cj is too large, use series filtering or place the TVS only on the power pins while protecting data lines with lower‑C alternatives.

How should engineers verify repetitive surge reliability for PTVS5V0S1UR?

Run repetitive‑pulse tests at expected energy levels with realistic intervals, monitor temperature rise and clamping stability, and ensure no latch‑up or degradation. Establish cool‑down intervals and device pass/fail criteria based on measured thermal recovery and electrical behavior.

© 2024 Engineering Technical Report Library. Optimized for GE/SEO. "Hand-drawn sketch, not precise schematic" - Non-exact representation for conceptual use.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- APT50GH120B Datasheet Deep Dive: Specs, Ratings & Curves

- BCM52311A1HH0H275S Datasheet Deep Dive: Key Specs & Metrics

- TL431IDBZR Performance Report: Measured Specs & Limits

- TL431BQDBZR Performance Report: Specs, Thermal Data

- TL431BMFDT datasheet: key specs, tolerances, variants

- TL431BIDBZR: Detailed Specs & Performance Report and Ratings

- TL431AQDBZR Specs Deep Dive: Key Limits & Pinout Explained

- TL431AIDBZR Performance Report: Key Specs & Benchmarks

-

S6008LLittelfuse Inc.SCR 600V 8A TO220

S6008LLittelfuse Inc.SCR 600V 8A TO220 -

CFR-12JB-52-110RYAGEORES 110 OHM 5% 1/6W AXIAL

CFR-12JB-52-110RYAGEORES 110 OHM 5% 1/6W AXIAL -

ECS-F1CE225KPanasonic Electronic ComponentsCAP TANT 2.2UF 20% 16V RADIAL

ECS-F1CE225KPanasonic Electronic ComponentsCAP TANT 2.2UF 20% 16V RADIAL -

ECS-F1HE475KPanasonic Electronic ComponentsCAP TANT 4.7UF 20% 50V RADIAL

ECS-F1HE475KPanasonic Electronic ComponentsCAP TANT 4.7UF 20% 50V RADIAL -

ECS-F1HE335KPanasonic Electronic ComponentsCAP TANT 3.3UF 20% 50V RADIAL

ECS-F1HE335KPanasonic Electronic ComponentsCAP TANT 3.3UF 20% 50V RADIAL -

ECS-F1HE155KPanasonic Electronic ComponentsCAP TANT 1.5UF 20% 50V RADIAL

ECS-F1HE155KPanasonic Electronic ComponentsCAP TANT 1.5UF 20% 50V RADIAL -

CFR-50JB-52-1RYAGEORES 1 OHM 5% 1/2W AXIAL

CFR-50JB-52-1RYAGEORES 1 OHM 5% 1/2W AXIAL -

MM74HC4050NonsemiIC BUFFER NON-INVERT 6V 16-PDIP

MM74HC4050NonsemiIC BUFFER NON-INVERT 6V 16-PDIP -

CFR-50JB-52-1KYAGEORES 1K OHM 5% 1/2W AXIAL

CFR-50JB-52-1KYAGEORES 1K OHM 5% 1/2W AXIAL -

CFR-25JB-52-1KYAGEORES 1K OHM 5% 1/4W AXIAL

CFR-25JB-52-1KYAGEORES 1K OHM 5% 1/4W AXIAL