-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

BCM52311A1HH0H275S Datasheet Deep Dive: Key Specs & Metrics

The BCM52311A1HH0H275S ships in a 1152‑pin PBGA package and is specified as Broadcom’s Knowledge‑Based Processor (KBP) for high‑speed, large‑rule database operations. This deep dive translates the BCM52311A1HH0H275S datasheet into actionable design guidance: engineers and procurement teams will learn the critical electrical and mechanical specs, performance metrics, PCB integration tips, and a concise buyer’s checklist. The article emphasizes where to read the datasheet tables for package, power, thermal, and lookup‑performance numbers and how to convert those specs into system‑level requirements and validation tests.

Readers will be able to extract package and pinout constraints, compute power budget and cooling needs from θJA/θJC values, map lookup capacity and latency to real‑world throughput, and follow a methodical integration checklist for power sequencing, signal integrity, and supply sourcing. Throughout, references are made to the official Broadcom datasheet as the primary source for absolute ratings and mechanical drawings; designers should consult that PDF for final sign‑off values.

1 — Product Overview & Context (Background)

1.1 What the BCM52311A1HH0H275S is (scope & role)

Point: The BCM52311A1HH0H275S is a Knowledge‑Based Processor (KBP) optimized for high‑rule, low‑latency lookup workloads common in telecom, routing, and security appliances. Evidence: The datasheet classifies the device as a KBP family member with hardware‑accelerated prefix and exact matching and large rule capacity. Explanation: For system architects, that means the chip offloads table‑lookup work from the main CPU and provides deterministic lookup latency under heavy rule sets, improving forwarding and policy‑enforcement scalability. Link: Designers should verify the functional summary in the official Broadcom datasheet to align expectations for rule types supported (exact, longest‑prefix, ternary if listed) and the interface model for host connectivity.

1.2 Part number breakdown & common variants

Point: The part suffix (A1/A0, HH0H275S style) encodes revision, package, and screening information—vital for BOM accuracy. Evidence: The datasheet and Broadcom ordering guides list part‑number fields for product family, silicon revision, package option, and temperature screening. Explanation: Practically, verify the full top‑mark and ordering code on vendor pages and in procurement workflows to avoid cross‑shipping variants with different power or thermal limits. Action: Use a two‑step method—match the full part string on the vendor quote and cross‑check the datasheet revision and package code in the Broadcom product listing before approving purchase orders.

1.3 Where it fits in Broadcom portfolio & competitor context

Point: The BCM52311 sits among KBP class devices and competes against TCAM/FPGA‑based solutions for large rule tables. Evidence: Broadcom positions KBP silicon for deterministic, energy‑efficient lookups versus TCAM’s power and FPGA’s flexibility. Explanation: Select this part when deterministic latency, predictable rule scaling, and a compact PCB implementation are priorities—choose FPGA when customization or algorithm changes are frequent, and TCAM when ternary matching density is mandatory. Action: Recommend target system profiles—carrier edge routers and security appliances that require millions of rules with tight latency budgets.

2 — Key Electrical & Mechanical Specs (At‑a‑Glance)

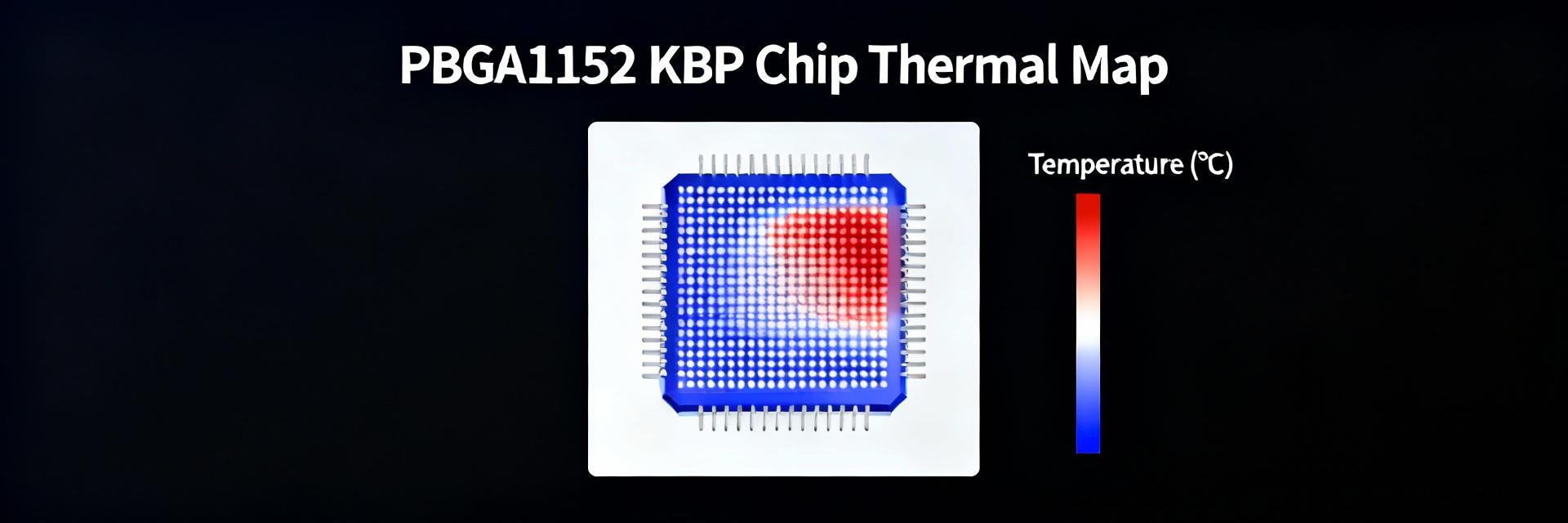

2.1 Package, pinout & mechanical details

Point: Expect PBGA1152 (1152‑pin) packaging with a specific ball map and detailed mechanical drawings. Evidence: The datasheet provides the package type, detailed ball‑map references, recommended footprint, and tolerance tables. Explanation: Extract the package outline and ball‑land pattern early in board design; follow the recommended solder mask expansion, keepout zones, and mounting notes to avoid assembly and reflow issues. Action: Pull the mechanical drawing from the datasheet to derive the board footprint and verify the land pattern with your OSAT; ensure the assembly house uses the recommended stencil apertures and reflow profile.

2.2 Power rails, voltage ranges & consumption specs

Point: The device defines multiple supply rails with nominal voltages, min/max tolerances, and typical/worst‑case currents for active and idle states. Evidence: The datasheet lists core, I/O, and auxiliary rail voltages and tabulates typical and maximum current consumption across operating modes. Explanation: Translate those currents into a system‑level power budget including PMIC headroom and connector limits. Action: Identify the minimum decoupling recommendations and power‑sequencing requirements in the datasheet; size bulk storage and transient decoupling to handle inrush and peak lookup bursts, and choose PMICs that support the specified soft‑start and sequencing order.

2.3 Thermal & environmental ratings

Point: Tj, Ta, and Tcase ranges plus thermal resistances (θJA/θJC) and recommended thermal solution guidance are provided. Evidence: The datasheet includes absolute maximum junction temperature, operating ambient limits, and θJA/θJC values for the PBGA package under defined board attachment conditions. Explanation: Use θJA to estimate steady‑state PCB temperature rise from power dissipation; compute required heatsink or forced‑air cooling to keep Tj below derated limits under worst‑case ambient. Action: Apply the datasheet’s thermal model and recommended board copper area and via stitching to meet thermal targets during layout.

3 — Performance Metrics & Benchmarks (Data Analysis)

3.1 Rule capacity, lookup latency & throughput metrics

Point: Key KBP metrics are maximum rule capacity, supported lookup types, per‑lookup latency, and aggregate lookups‑per‑second. Evidence: The datasheet specifies maximum entries per table, supported match types (exact/prefix/other), and latency figures under nominal conditions. Explanation: Convert these numbers to system behavior—determine if the device meets per‑packet latency budgets and sustained lookup throughput for target traffic profiles. Action: Map rules per second by combining lookup latency and internal parallelism; plan for headroom to prevent latency spikes under concurrent control plane activity.

3.2 Interface bandwidth & supported protocols

Point: On‑chip interfaces (host bus, serial links, DDR/QDR interfaces if present) set aggregate bandwidth and must match system backplanes. Evidence: The datasheet lists supported interfaces, lane counts, and per‑lane throughput, plus bus protocols and endianness. Explanation: Compute aggregate ingress/egress bandwidth requirements by summing per‑lane rates; ensure the host processor or switch ASIC can sustain command and data rates without creating an I/O bottleneck. Action: When sizing queues and DMA engines, use the datasheet’s protocol timing and throughput numbers to avoid interface saturation.

3.3 Timing, clocks & performance scaling

Point: Clock domains, recommended reference frequencies, and performance scaling with clock and thread settings are documented. Evidence: The datasheet provides clocking recommendations, jitter tolerances, and notes on whether additional PLLs or timing reference devices are required. Explanation: Clock selection affects lookup latency and throughput; mismatched clock domains can introduce metastability or reduce effective performance. Action: Include recommended clock trees and test multiple clock settings in the lab to validate how performance scales with frequency and concurrency settings.

4 — Integration & PCB Design Guidelines (Method/How‑to)

4.1 Power sequencing, supply filtering & decoupling

Point: The datasheet prescribes the order of rail application, recommended capacitor types, and placement tolerances. Evidence: Typical guidance includes sequencing diagrams, decoupling capacitance per rail, and ESR/ESL recommendations. Explanation: Proper sequencing prevents latchups and protects IOs and core logic; correct decoupling stabilizes rails against transient currents from lookup bursts. Action: Implement PMICs that support required sequencing and programmable ramps; place bulk and high‑frequency decoupling adjacent to corresponding pins per the datasheet’s placement map.

4.2 Signal integrity & layout tips for PBGA1152

Point: High‑speed lanes require controlled impedance, careful BGA escape routing, and skew control for differential pairs. Evidence: The datasheet and application notes typically recommend stackups, pair spacing, and via strategies for the PBGA1152 footprint. Explanation: Use microstrip/stripline stackups to control impedance; stagger escape vias to reduce congestion and follow recommended pair length matching to meet timing. Action: Define a 6–8 layer stackup with dedicated power/ground planes, specify differential trace impedance (e.g., 90Ω±10% or as recommended), and validate with pre‑layout SI simulations.

4.3 Thermal management & mechanical considerations

Point: Heatsink mounting, thermal via arrays, airflow direction, and PCB copper area recommendations reduce θJA. Evidence: The datasheet gives recommended thermal via patterns and board copper pour guidance to meet thermal spec. Explanation: Distribute power dissipating zones and place thermal vias under the PBGA thermal pad to extract heat into internal planes; use forced convection when natural convection is insufficient. Action: Perform a quick thermal calc: P_dissipation × θJA + ambient ≤ Tj_max margin; validate with IR imaging and thermocouple probes during bring‑up.

5 — Use Cases, Reference Designs & Compliance Notes (Case study)

5.1 Typical deployment scenarios & system architectures

Point: Typical deployments include edge routers, carrier switches, and security appliances requiring large rule tables and deterministic lookup latency. Evidence: The device’s KBP designation and datasheet capacity/latency metrics suggest these fits. Explanation: In an edge router, the KBP performs route/ACL lookups in hardware to reduce CPU load; in security appliances, it accelerates policy enforcement at line rate. Action: Prioritize this part for systems where rule density and predictable latency are higher priorities than field‑programmable flexibility.

5.2 Reference boards, evaluation kits & firmware resources

Point: Broadcom provides reference designs and evaluation platforms—validate EVM firmware and example toolchains against production needs. Evidence: Reference schematics and EVM feature lists typically accompany the datasheet and product brief. Explanation: Use the evaluation board to confirm power sequencing, thermal behavior, and interface compatibility before committing to production PCB spins. Action: Checklist for EVM testing: verify power sequencing, run sustained lookup benchmarks, validate interface throughput, and confirm memory and host interoperability.

5.3 Regulatory & lifecycle considerations

Point: Compliance notes—RoHS, lead‑free status, and JEDEC/IPC packaging standards—appear in product documentation; lifecycle and availability cues (EOL notices) must be tracked. Evidence: The datasheet and Broadcom product documents indicate environmental compliance and suggest typical lead times. Explanation: Long‑lived telecom platforms require lifecycle assurance—confirm that sourcing channels and Broadcom’s availability roadmaps align with product lifecycle. Action: Procurement should request availability certificates and consider dual‑sourcing strategies or last‑time buy planning if risk appears.

6 — Troubleshooting, Procurement & Buyer's Checklist (Actionable checklist)

6.1 Common integration pitfalls & debug checklist

Point: Frequent integration issues include incorrect power sequencing, clocking mismatches, and inadequate thermal dissipation. Evidence: Datasheet absolute max ratings and sequencing diagrams define failure modes when violated. Explanation: Use a structured debug flow: verify PMIC rails with scope, confirm clock frequencies and jitter, monitor temperature during load tests, and isolate I/O faults with loopback tests. Action: Must‑test items during bring‑up include power‑rail ramp timing, basic heartbeat interface, memory/host link training, and a thermal soak test at worst‑case power.

6.2 Sourcing, part equivalence & packaging concerns

Point: Confirm genuine Broadcom parts and package traceability to avoid counterfeit or mismatched revisions. Evidence: Distributor part data and lot codes, plus Broadcom ordering information, are the authoritative sources. Explanation: Validate package markings, date codes, and cross‑reference revision letters to the datasheet; mismatches can silently change thermal or electrical margins. Action: Maintain a short list of authorized distributors, require certificate of conformance, and include lot code checks as part of incoming inspection.

6.3 Final pre‑production datasheet verifications

Point: Before first article, verify pinout, absolute max ratings, derating margins, and mechanical tolerances. Evidence: The datasheet gives pin assignments, voltage/current limits, and mechanical tolerances that define acceptance criteria. Explanation: A final signoff ensures that the board footprint, power budget, and thermal design meet the device’s limits with safety margins. Action: Use a signoff checklist that includes pin mapping, power budget review (with 20–30% headroom), thermal validation plan, and mechanical tolerance confirmation for assembly.

Summary / Conclusion (use keywords 1×; 160–220 words)

This deep dive highlights where to find the critical BCM52311A1HH0H275S datasheet entries and how to convert them into system‑level decisions. The top three specs to validate during selection and design are package & pinout (PBGA1152 footprint and ball map), power/thermal (rail voltages, consumption, and θJA/θJC), and performance metrics (rule capacity, lookup latency, and interface bandwidth). Immediate next steps for engineers are: download the official Broadcom datasheet, order an evaluation module to validate sequencing and throughput, and schedule thermal and power tests under worst‑case conditions. Before committing to production, confirm sourcing availability and verify part‑markings and lot codes with authorized distributors. Always compare datasheet tolerances to system margins and document signoff criteria for power, thermal, and mechanical acceptance.

- Validate package & pinout from the datasheet; ensure PBGA1152 land pattern and assembly profile match manufacturing capabilities.

- Compute power budget and thermal dissipation using datasheet θJA figures; plan heatsinking or airflow to maintain safe junction temperatures.

- Map rule capacity and lookup latency to expected traffic—confirm interface bandwidth avoids host bottlenecks.

- Use an EVM to verify sequencing, clocks, and sustained throughput before PCB finalization.

- Require distributor traceability and datasheet revision matching to avoid part‑equivalence errors.

Frequently Asked Questions

1 — Where can I get the official BCM52311A1HH0H275S datasheet?

Answer: The official datasheet and product documentation are available from Broadcom’s technical documentation portal and should be the primary source for absolute ratings, mechanical drawings, and electrical tables. Engineers should download the latest PDF, confirm the document revision on the datasheet cover, and use its tables for pinout, power, thermal, and performance claims during design and procurement.

2 — What are the most important specs in the BCM52311A1HH0H275S datasheet to check for thermal design?

Answer: Focus on θJA and θJC values, maximum junction temperature (Tj_max), typical power dissipation at target workloads, and recommended board copper/thermal via patterns. Use θJA × power_dissipation + ambient_temp to estimate junction temperature and design heatsink or airflow to keep Tj below the datasheet’s derated operating limit. Validate with IR imaging and thermocouple measurements during lab tests.

3 — How many rules and what lookup latency can I expect from BCM52311A1HH0H275S?

Answer: The datasheet lists maximum entries per table and nominal lookup latency under defined conditions—use those figures to determine whether the device meets application throughput and latency budgets. Translate latency and internal parallelism into rules‑per‑second capacity for your workload, and add headroom for control‑plane operations and concurrent access patterns when sizing system resources.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- APT50GH120B Datasheet Deep Dive: Specs, Ratings & Curves

- BCM52311A1HH0H275S Datasheet Deep Dive: Key Specs & Metrics

- TL431IDBZR Performance Report: Measured Specs & Limits

- TL431BQDBZR Performance Report: Specs, Thermal Data

- TL431BMFDT datasheet: key specs, tolerances, variants

- TL431BIDBZR: Detailed Specs & Performance Report and Ratings

- TL431AQDBZR Specs Deep Dive: Key Limits & Pinout Explained

- TL431AIDBZR Performance Report: Key Specs & Benchmarks

-

S6008LLittelfuse Inc.SCR 600V 8A TO220

S6008LLittelfuse Inc.SCR 600V 8A TO220 -

CFR-12JB-52-110RYAGEORES 110 OHM 5% 1/6W AXIAL

CFR-12JB-52-110RYAGEORES 110 OHM 5% 1/6W AXIAL -

ECS-F1CE225KPanasonic Electronic ComponentsCAP TANT 2.2UF 20% 16V RADIAL

ECS-F1CE225KPanasonic Electronic ComponentsCAP TANT 2.2UF 20% 16V RADIAL -

ECS-F1HE475KPanasonic Electronic ComponentsCAP TANT 4.7UF 20% 50V RADIAL

ECS-F1HE475KPanasonic Electronic ComponentsCAP TANT 4.7UF 20% 50V RADIAL -

ECS-F1HE335KPanasonic Electronic ComponentsCAP TANT 3.3UF 20% 50V RADIAL

ECS-F1HE335KPanasonic Electronic ComponentsCAP TANT 3.3UF 20% 50V RADIAL -

ECS-F1HE155KPanasonic Electronic ComponentsCAP TANT 1.5UF 20% 50V RADIAL

ECS-F1HE155KPanasonic Electronic ComponentsCAP TANT 1.5UF 20% 50V RADIAL -

CFR-50JB-52-1RYAGEORES 1 OHM 5% 1/2W AXIAL

CFR-50JB-52-1RYAGEORES 1 OHM 5% 1/2W AXIAL -

MM74HC4050NonsemiIC BUFFER NON-INVERT 6V 16-PDIP

MM74HC4050NonsemiIC BUFFER NON-INVERT 6V 16-PDIP -

CFR-50JB-52-1KYAGEORES 1K OHM 5% 1/2W AXIAL

CFR-50JB-52-1KYAGEORES 1K OHM 5% 1/2W AXIAL -

CFR-25JB-52-1KYAGEORES 1K OHM 5% 1/4W AXIAL

CFR-25JB-52-1KYAGEORES 1K OHM 5% 1/4W AXIAL