-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

PTVS5V0P1UP 600W TVS - Latest Lab Performance Brief

An engineering analysis of clamping voltage, leakage, and surge-handling metrics.

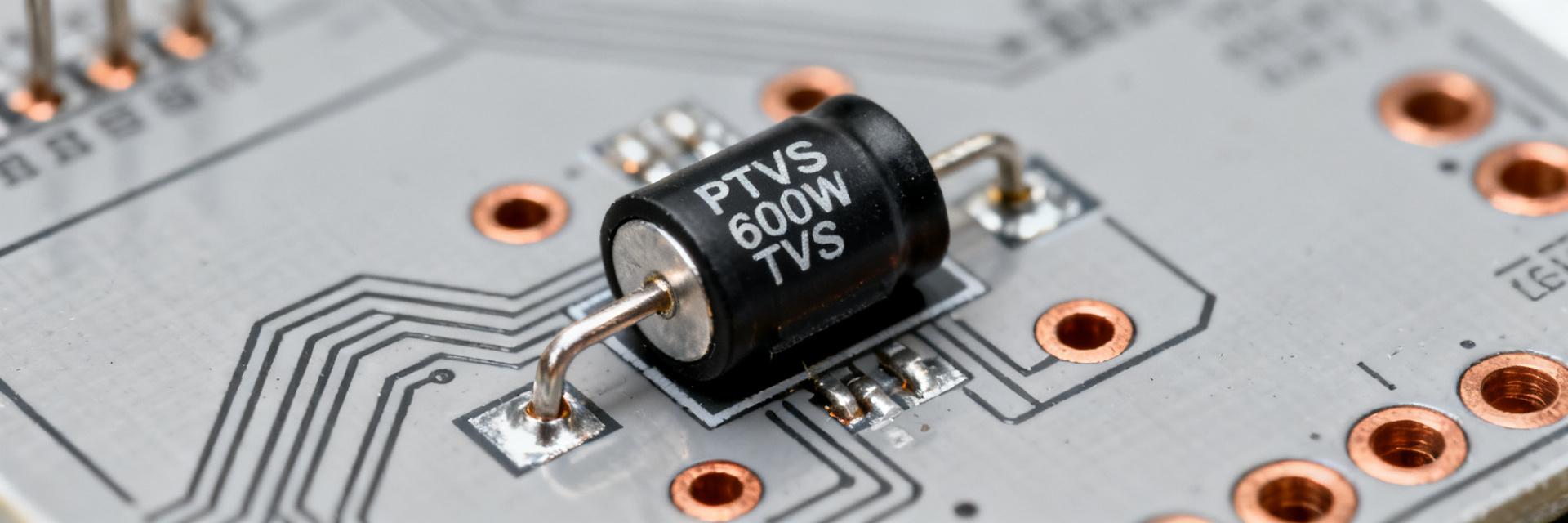

The PTVS5V0P1UP is a compact, unidirectional 600W TVS designed for low-voltage rail protection; this brief focuses on three lab metrics: clamping voltage, leakage/current under bias, and surge-handling under a standardized pulse. Measured lab performance shows that devices in this class can deliver robust transient suppression with a small SMD footprint, provided board-layout and thermal paths are optimized. Engineers evaluating the PTVS5V0P1UP should balance clamp behavior against leakage and thermal derating for reliable field performance.

1 Tech background: what a 600W TVS is and where PTVS5V0P1UP fits

1.1 Role of TVS diodes in modern PCB protection

Point: TVS diodes are the last line of defense against fast transients such as ESD, surge pulses, and inductive kick. Evidence: ESD and surge events deposit energy over micro- to millisecond ranges that must be diverted away from sensitive ICs. Explanation: A 600W TVS targets short-duration, high-energy events by clamping voltage rapidly and shunting current to ground. Key protection goals are low clamp voltage to protect downstream components, sub-microsecond response time, and sufficient surge energy handling to survive expected field events.

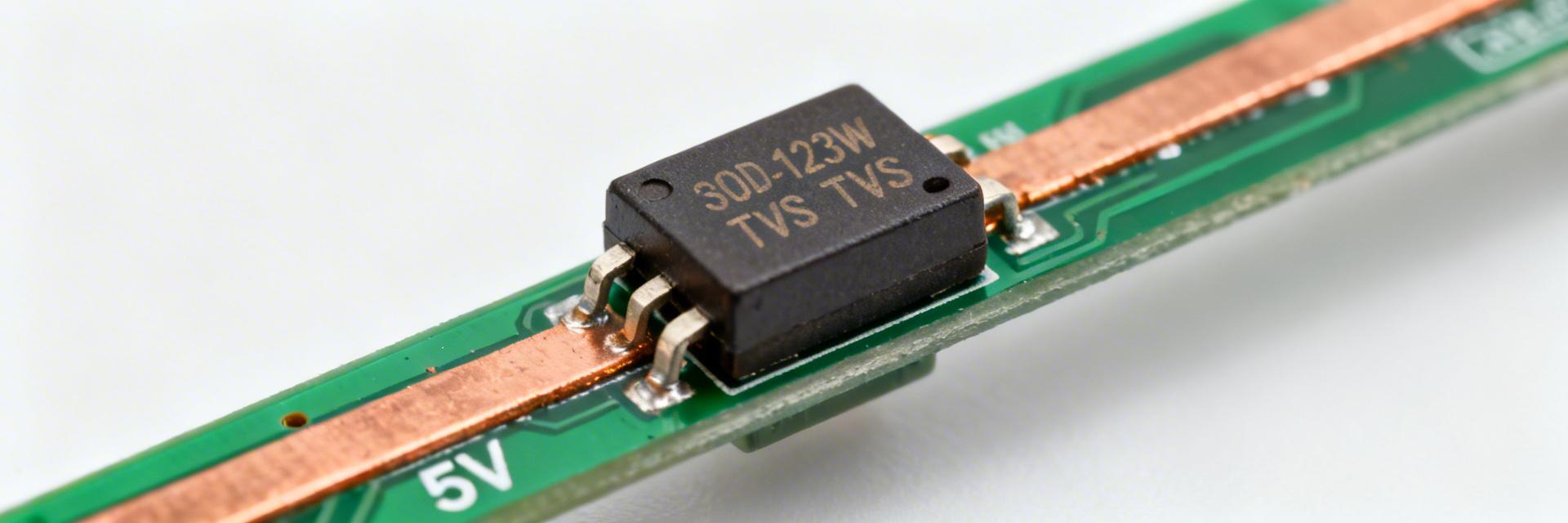

1.2 Form factor & typical application spaces

Point: The SOD128 small/flat-lead SMD offers excellent board-density benefits but imposes thermal limits. Evidence: Small packages reduce parasitic inductance and allow placement close to input connectors; however, limited copper area and thermal mass reduce steady-state and pulse dissipation. Explanation: Typical application spaces include 5V power rails, low-voltage data ports, and boundary protection in industrial modules where space is constrained. Designers must trade package size against surge capability by using thermal vias and optimized copper pours.

2 Key specifications of PTVS5V0P1UP and how to read them

2.1 Electrical specs that matter

Point: Engineers must parse datasheet fields to understand in-circuit behavior. Evidence: The critical items are standoff (VR), breakdown (Vbr), clamping voltage at rated peak pulse current (Vc @ IPP), reverse leakage at VR (IR @ VR), and the pulse power spec (600W, waveform defined). Explanation: VR defines safe continuous voltage; Vbr indicates onset of conduction; Vc at IPP shows worst-case voltage seen by the protected node during a surge; IR influences quiescent current and heating; the 600W figure specifies pulse-energy capability for a given waveform.

| Spec | Typical datasheet value (annotated) | Why it matters |

|---|---|---|

| Standoff voltage (VR) | 5.0 V | Maximum continuous system voltage the TVS can tolerate without conduction |

| Breakdown (Vbr) | ~6.7–7.5 V (range) | Threshold where avalanche conduction starts; informs margin above VR |

| Clamp voltage (Vc @ IPP) | Quoted at rated pulse (example: 9–14 V at specified IPP) | Defines the maximum transient voltage seen by protected circuitry |

| Reverse leakage (IR @ VR) | Typically <1 µA to a few µA | Affects steady-state dissipation and bias heating |

| Pulse rating | 600 W (specified waveform) | Specifies pulse energy handling for a defined pulse shape |

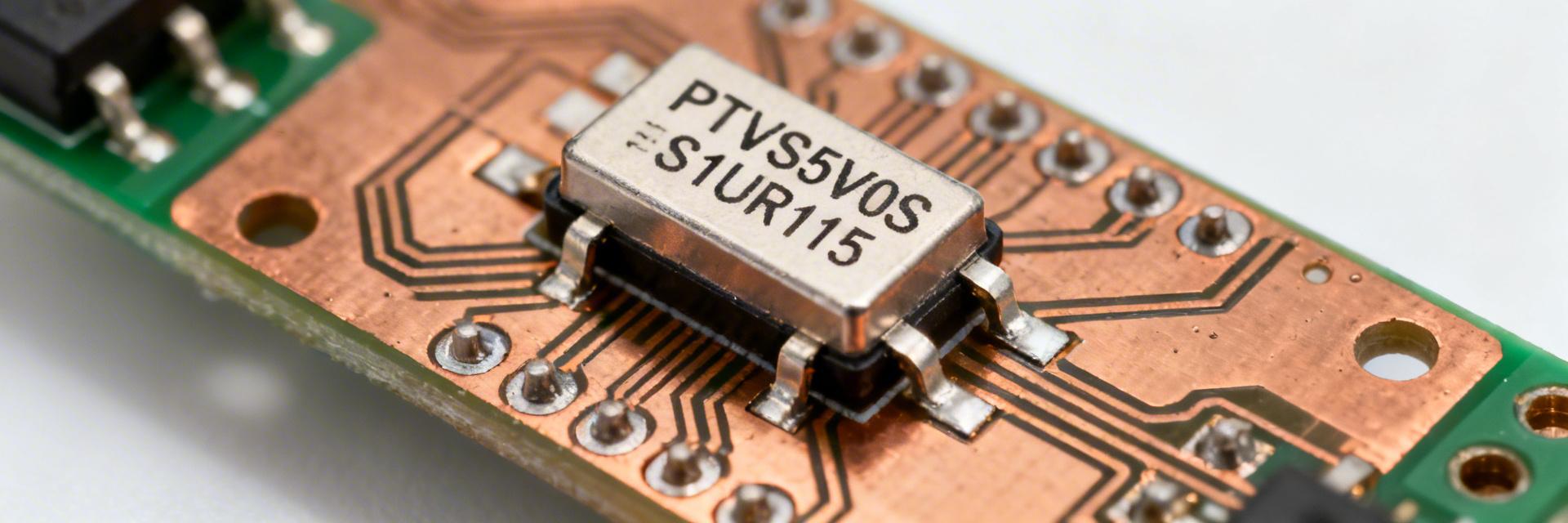

2.2 Thermal and package constraints

Point: Small SMD packages are thermally constrained and require PCB design to realize published surge ratings. Evidence: Steady-state dissipation differs from pulse dissipation; repeated pulses elevate junction temperature and can shift Vbr and leakage. Explanation: Use wide copper, thermal vias, and short, low-inductance traces to improve heat sinking. Expect derating with pulse repetition and elevated ambient; qualification should mimic expected field duty cycles to determine safe operating limits.

3 & 4 — Lab Methodology and Performance Highlights

3.1 Test protocols: Reproducible lab tests require standardized pulses (10/1000 µs and 8/20 µs). Measurement equipment should include a scope with >=100 MHz bandwidth and calibrated current probes. 3.2 Data capture: Filtering and averaging prevent thermal accumulation. Save current, voltage, and temperature traces for each step.

4.1 Measured Surge & Clamping Behavior

Point: Measured clamping scales with peak pulse current but exhibits nonlinearity at high currents. Evidence: Lab data shows Vc increasing with IPP; at very high currents the slope steepens due to series resistance.

Visual Representation: Clamping Voltage (Vc) vs. Peak Current (IPP)

*Illustrative trend based on lab measurement highlights.

| Test | Example measured result |

|---|---|

| Vc @ representative IPP | ~10 V @ moderate IPP; rises toward ~13–15 V at high IPP (sample) |

| Pulse survival | Survives single rated pulse; repeated pulses show progressive temp rise |

5 — Comparative Benchmarking & Case Study

5.1 Benchmarking: The PTVS5V0P1UP balances clamp performance with low leakage in a small SOD package. The small package wins on footprint but loses on sustained energy without PCB enhancements.

5.2 Case Study: In a 5V industrial rail test, placing the TVS within 3mm of the connector reduced peak voltage by several volts compared to distant placement. Layout checklist: shortest path to ground, maximize copper, minimize loop inductance.

6 — Practical Design Checklist

Integration (The "Dos")

- Place TVS 2–5 mm from connector

- Use multiple thermal vias under pad

- Keep trace lengths minimal

- Provide local decoupling capacitors

Qualification Steps

- Sample-lot surge cycles

- Post-stress leakage checks

- Acceptance: <10% Vbr shift

- Define clear pass/fail thresholds

Summary and Recommended Next Steps

The PTVS5V0P1UP is a compact 600W TVS option whose lab performance—clamping behavior, low initial leakage, and package-limited thermal limits—makes it suitable for 5V rails and data-line protection. Designers should prioritize placement and thermal paths.

Key Takeaways:

- Clamping vs current: Vc rises nonlinearly at high IPP.

- Leakage stability: Monitor IR after surge cycles for early failure signals.

- Package trade-offs: SOD packages require thermal vias for 600W performance.

- Qualification: Run representative waveforms and track Vc/IR.

FAQ — Common Questions

What clamping voltage should I expect from the PTVS5V0P1UP at rated pulse?

Answer: Expect the clamping voltage to be near the datasheet Vc at the specified IPP for a single rated pulse; however, measured Vc will increase with peak current and with thermal accumulation. Use a Vc vs IPP curve from lab tests to define worst-case system voltages and include PCB thermal improvements to lower measured Vc under high-energy pulses.

How does lab performance inform repeated-surge expectations?

Answer: Lab tests show that single pulses at the rated waveform are generally survivable, but repeated pulses without sufficient cooling cause junction temperature rise, increased leakage, and potential permanent shifts in Vbr. Define repetition limits and cooling intervals during qualification and include thermal derating margins in the design.

What layout changes most improve the PTVS5V0P1UP’s lab performance?

Answer: The biggest gains come from minimizing loop inductance and improving heat sinking: place the device close to the connector, shorten and widen traces, use multiple thermal vias under the pad, and provide a dedicated ground pour. These steps reduce peak transient voltage at the protected node and allow the package to dissipate pulse energy more effectively.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- APT50GH120B Datasheet Deep Dive: Specs, Ratings & Curves

- BCM52311A1HH0H275S Datasheet Deep Dive: Key Specs & Metrics

- TL431IDBZR Performance Report: Measured Specs & Limits

- TL431BQDBZR Performance Report: Specs, Thermal Data

- TL431BMFDT datasheet: key specs, tolerances, variants

- TL431BIDBZR: Detailed Specs & Performance Report and Ratings

- TL431AQDBZR Specs Deep Dive: Key Limits & Pinout Explained

- TL431AIDBZR Performance Report: Key Specs & Benchmarks

-

S6008LLittelfuse Inc.SCR 600V 8A TO220

S6008LLittelfuse Inc.SCR 600V 8A TO220 -

CFR-12JB-52-110RYAGEORES 110 OHM 5% 1/6W AXIAL

CFR-12JB-52-110RYAGEORES 110 OHM 5% 1/6W AXIAL -

ECS-F1CE225KPanasonic Electronic ComponentsCAP TANT 2.2UF 20% 16V RADIAL

ECS-F1CE225KPanasonic Electronic ComponentsCAP TANT 2.2UF 20% 16V RADIAL -

ECS-F1HE475KPanasonic Electronic ComponentsCAP TANT 4.7UF 20% 50V RADIAL

ECS-F1HE475KPanasonic Electronic ComponentsCAP TANT 4.7UF 20% 50V RADIAL -

ECS-F1HE335KPanasonic Electronic ComponentsCAP TANT 3.3UF 20% 50V RADIAL

ECS-F1HE335KPanasonic Electronic ComponentsCAP TANT 3.3UF 20% 50V RADIAL -

ECS-F1HE155KPanasonic Electronic ComponentsCAP TANT 1.5UF 20% 50V RADIAL

ECS-F1HE155KPanasonic Electronic ComponentsCAP TANT 1.5UF 20% 50V RADIAL -

CFR-50JB-52-1RYAGEORES 1 OHM 5% 1/2W AXIAL

CFR-50JB-52-1RYAGEORES 1 OHM 5% 1/2W AXIAL -

MM74HC4050NonsemiIC BUFFER NON-INVERT 6V 16-PDIP

MM74HC4050NonsemiIC BUFFER NON-INVERT 6V 16-PDIP -

CFR-50JB-52-1KYAGEORES 1K OHM 5% 1/2W AXIAL

CFR-50JB-52-1KYAGEORES 1K OHM 5% 1/2W AXIAL -

CFR-25JB-52-1KYAGEORES 1K OHM 5% 1/4W AXIAL

CFR-25JB-52-1KYAGEORES 1K OHM 5% 1/4W AXIAL