-

帮助您节省成本和时间。

帮助您节省成本和时间。 -

为您的货物提供可靠的包装。

为您的货物提供可靠的包装。 -

快速可靠的交付以节省时间。

快速可靠的交付以节省时间。 -

优质的售后服务。

优质的售后服务。

博客

零件编号

热门零件

最新零件

-

BCM52311A1HH0H275S

-

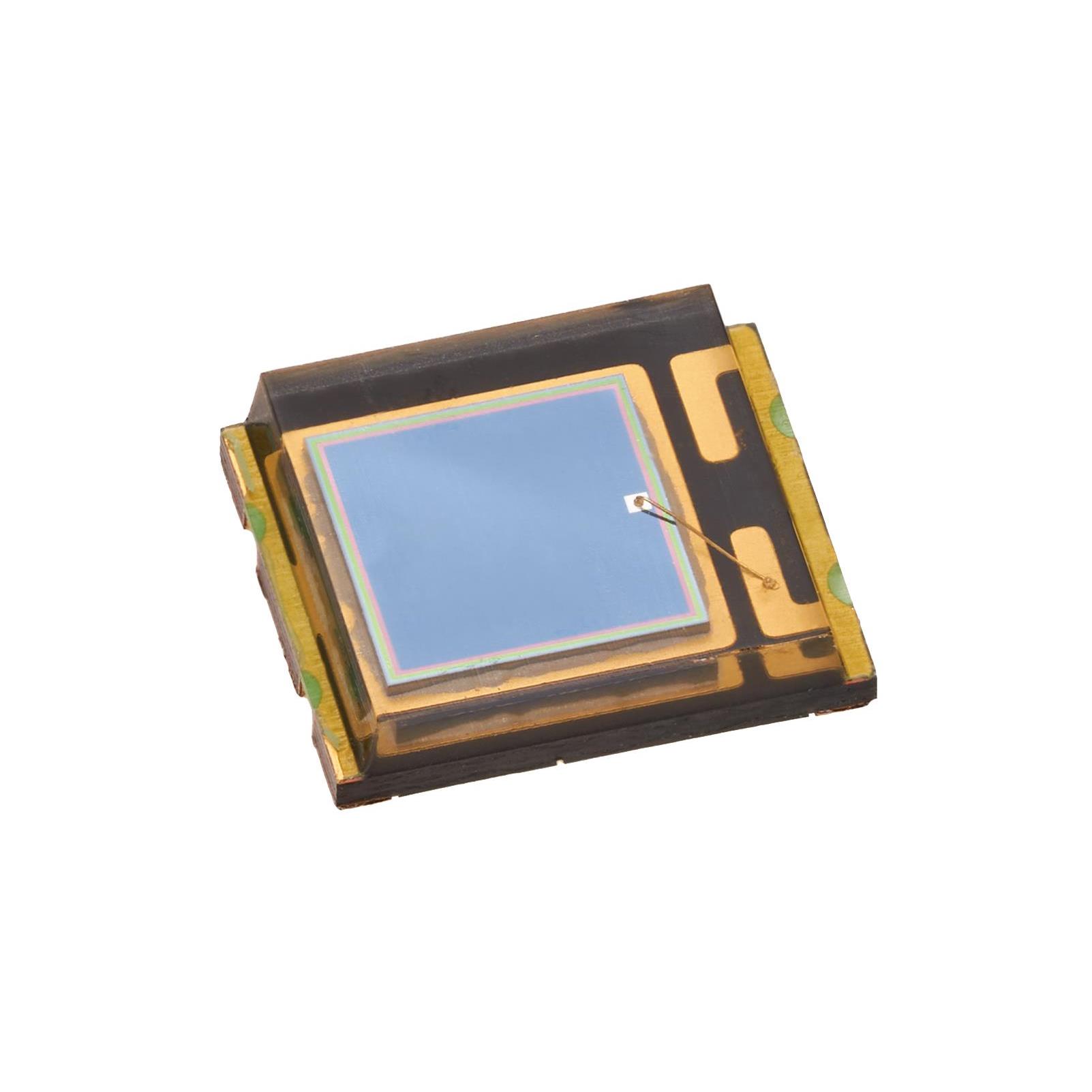

APDS-9160-003

-

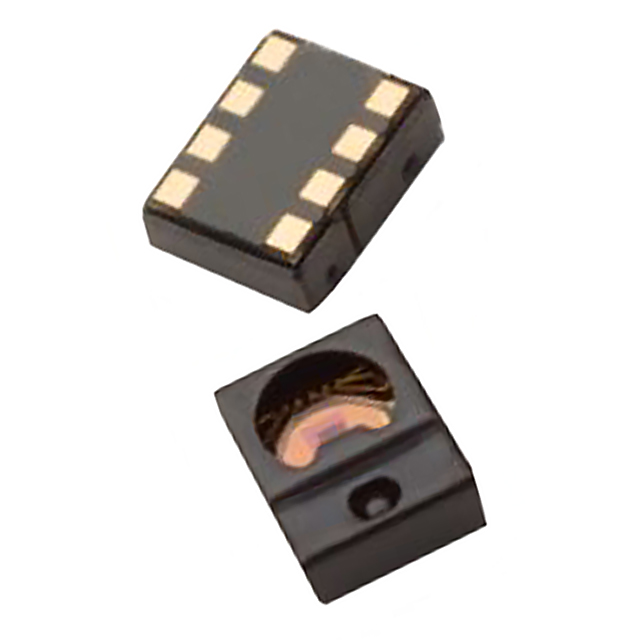

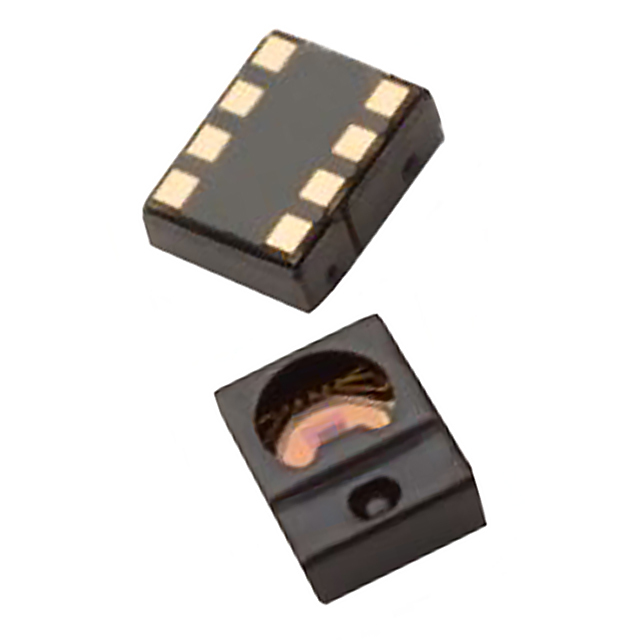

APDS-9151

-

ACPL-C740-500E

-

ACPL-C740-000E

-

ACPL-0873-500E

-

ASMW-LWG0-NEGFE

-

ASMW-LWG0-NEGDE

-

ASMW-LWG0-NEGBE

-

ASMW-LWG0-NDFHE

-

ASMW-LL00-NKM0E

-

ASMW-LD00-AGJ0E

-

ASMW-L300-AFH0E

-

ASMB-LTD2-0A333

-

ASMB-LTC2-0A335

-

QK016NH6RP

-

D50K5R0

-

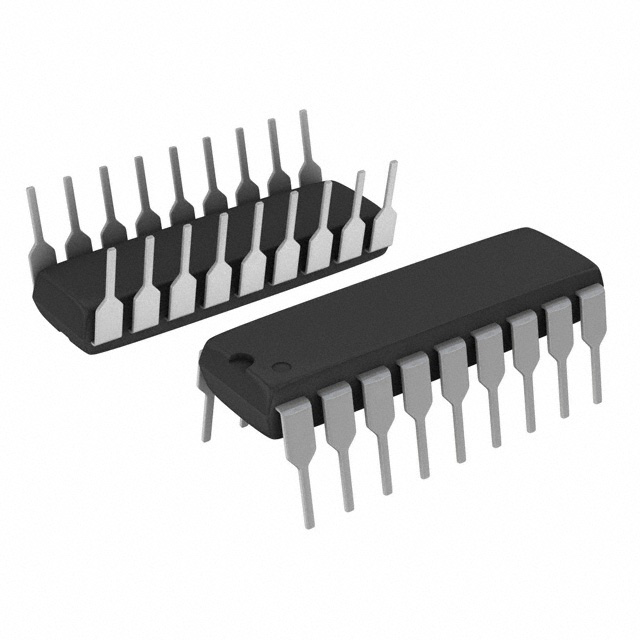

M74HCT374RM13TR

-

D25K100

-

VS-40HFL10S02

-

TLV2470AIDR

-

TPS2015P

-

VS-16FLR10S02

-

RHS10K

-

L6004V3TP

-

UC2637N

-

SWT-1.02-168

-

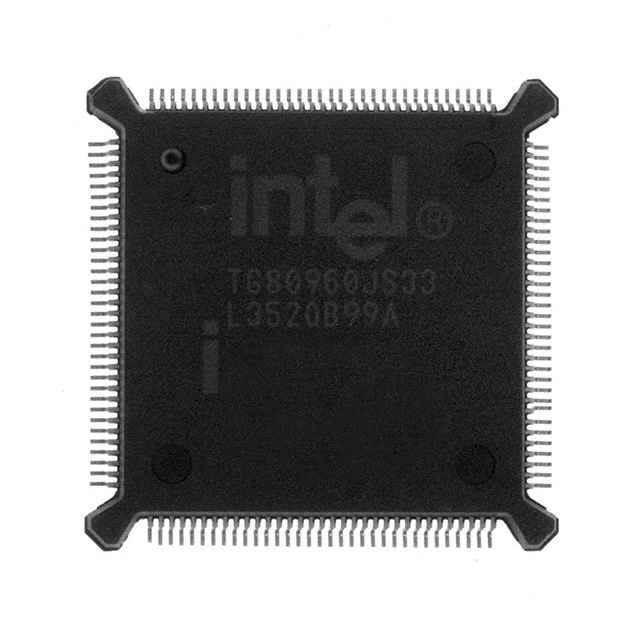

TG80960JS33

-

K2200G

-

VS-85HFL100S05