-

帮助您节省成本和时间。

帮助您节省成本和时间。 -

为您的货物提供可靠的包装。

为您的货物提供可靠的包装。 -

快速可靠的交付以节省时间。

快速可靠的交付以节省时间。 -

优质的售后服务。

优质的售后服务。

博客

零件编号

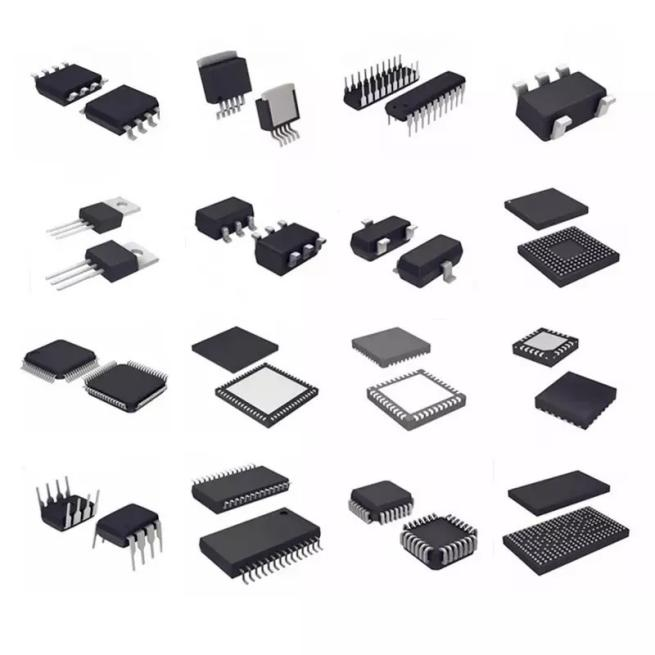

热门零件

最新零件

-

BCM52311A1HH0H275S

-

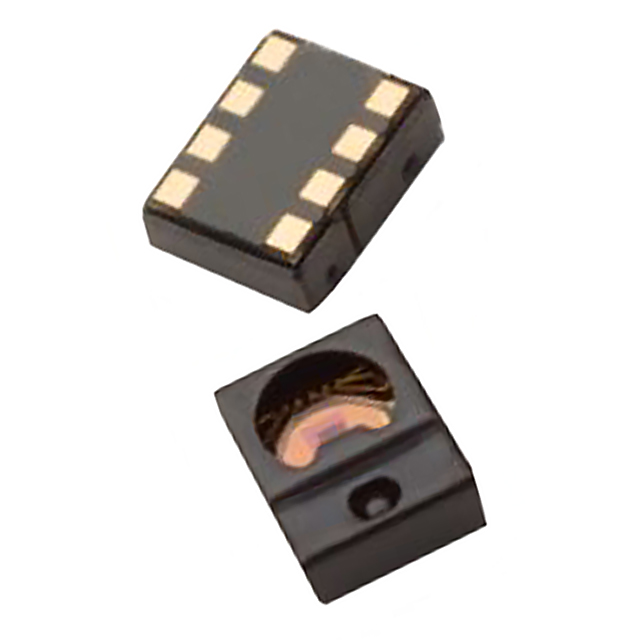

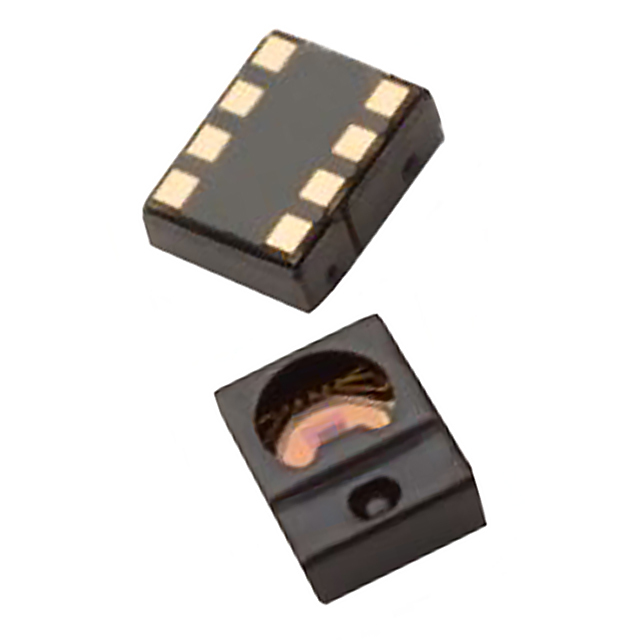

APDS-9160-003

-

APDS-9151

-

ACPL-C740-500E

-

ACPL-C740-000E

-

ACPL-0873-500E

-

ASMW-LWG0-NEGFE

-

ASMW-LWG0-NEGDE

-

ASMW-LWG0-NEGBE

-

ASMW-LWG0-NDFHE

-

ASMW-LL00-NKM0E

-

ASMW-LD00-AGJ0E

-

ASMW-L300-AFH0E

-

ASMB-LTD2-0A333

-

ASMB-LTC2-0A335

-

MS288-10S-NS

-

SCDR302W472K4GV001E

-

SMF110511R10LZF

-

PCM1H121MCL1GS

-

RAA808013GP3#JA0

-

EEF-TX0E391RC

-

MS288-10F-NS

-

SMF090610R18LZF

-

PCM1V151MCL1GS

-

EEF-KZ0D561RE

-

HOB 130-P/SP1

-

EEF-KX0J151RF

-

AL6-SMSFBW-9

-

SMF100512R17KZF

-

EFR32MR21A020F512IM32-CR